فروش پروژه اجرای FPGA به کمک LUT و ASIC برپایه یادگیری عمیق کانولوشن با MATLAB

کد پروژه: 3087

عنوان پروژه: فروش پروژه اجرای FPGA به کمک LUT و ASIC برپایه یادگیری عمیق کانولوشن با MATLAB

قالب بندی: m – mdl – داکیومنت

دسته: کامپیوتر – MATLAB

قیمت: 100.000 تومان

قابلیت اجرا در نرم افزار: MATLAB

شرح مختصر:

فروش پروژه اجرای FPGA به کمک LUT و ASIC برپایه یادگیری عمیق کانولوشن با MATLAB

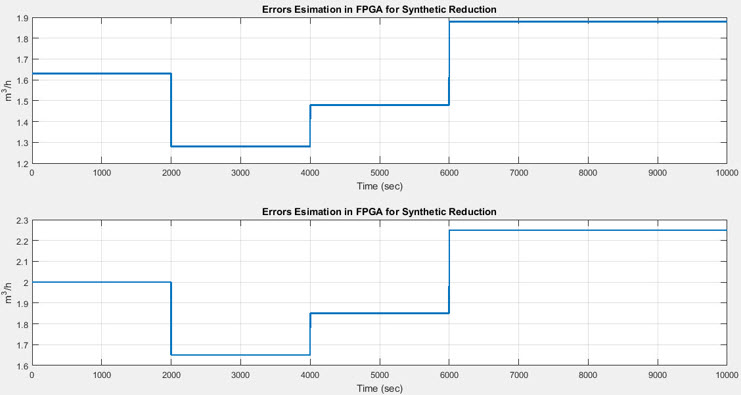

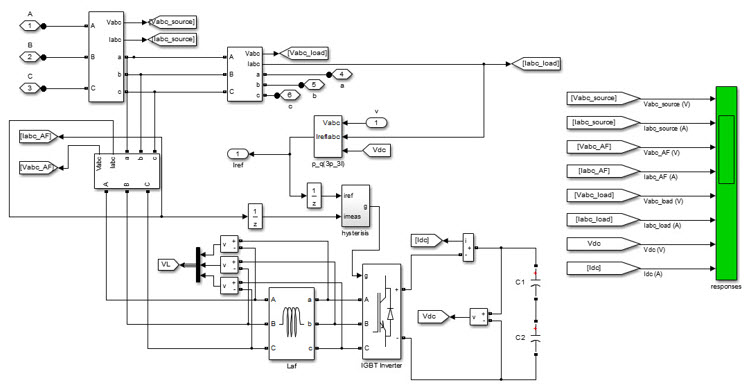

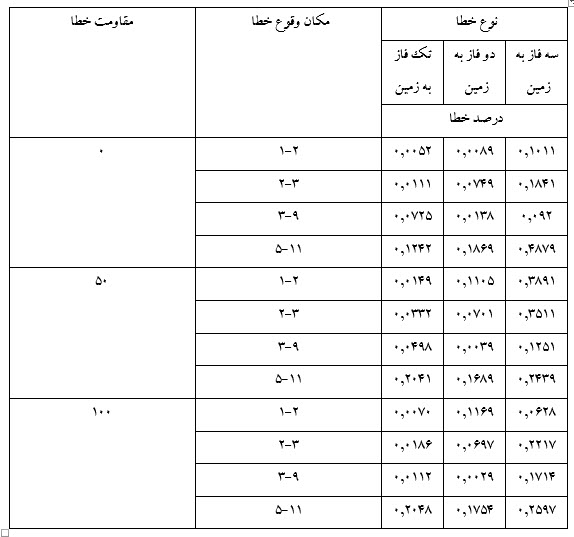

FPGA ها عمدتا برای طراحی مدارهای مجتمع ویژه برنامه (ASIC) استفاده می شوند. ابتدا معماری چنین مداری طراحی می شود. سپس، از یک FPGA برای ساخت و بررسی نمونه اولیه آن استفاده می گردد. خطاها قابل اصلاح هستند. هنگامی که نمونه اولیه مطابق انتظار عمل کرد، یک پروژه ASIC بر اساس طراحی FPGA ایجاد و تولید می شود. این امر امکان می دهد تا در زمان صرفه جویی شود، زیرا ساخت یک مدار مجتمع می تواند یک فرآیند بسیار پیچیده و زمان بر باشد. همچنین باعث صرفه جویی در هزینه می شود، زیرا می توان از یک FPGA برای تهیه بسیاری از تکرارهای همان پروژه استفاده کرد. در این زمینه شایان ذکر است که واحدهای پردازش تانسور مدرن (TPU) یا ماینرهای ارزهای دیجیتال ابتدا به عنوان FPGA طراحی شدند و تنها پس از بلوغ تولید شدند. FPGA ها همچنین در سیستم های بلادرنگ استفاده می شوند که زمان پاسخگویی، نقش مهمی د ر آن ها ایفا می کند. در CPUهای استاندارد، زمان پاسخگویی تنظیم نشده است و دقیقا مشخص نیست پس از ظاهر شدن سیگنال اولیه چه زمانی پاسخ دریافت خواهد شد. برای به حداقل رساندن یا حفظ آن در محدوده معین، از سیستم عامل های بلادرنگ استفاده می شود. با این حال، در سناریوهایی که زمان پاسخ سریع (زیر میلی ثانیه) ضروری است، این زمان کوتاه است. برای حل این مشکل، الگوریتم درخواستی باید با استفاده از منطق ترکیبی یا ترتیبی در FPGA پیاده سازی شود تا زمان پاسخگویی همیشه یکسان و کمتر از میلی ثانیه باشد. چنین سیستم بلادرنگ پیاده سازی شده در FPGA را می توان تغییر داد و پس از آماده شدن به تولید منتقل کرد. مدار یکپارچه ای که به این روش ایجاد می شود، بسیار سریعتر و کم مصرف تر خواهد بود. جدای از آن، FPGA ها در پروژه هایی استفاده می شوند که پیکربندی سخت افزاری در معرض تغییر است و مداری که می تواند با این تغییرات تنظیم شود، درخواست می گردد. در صورتی که تامین کنندگان سخت افزار تغییر یابد و سخت افزار جدید رابط مورد نیاز را نداشته باشد، FPGA به یک انتخاب طبیعی تبدیل می شود. در این تحقیق به اجرای FPGA به کمک جمع کننده های خط لوله پرداخته شده است که با در نظر گرفتن مولفه ها و تجهیزات RTL و ورودی های LUT، می توان به این امر در کاهش خطاها، کاهش سنتز، کاهش هزینه و انرژی و بهبود انعطاف پذیری و مقیاس پذیری، کمک نمود. برای همین امر، هدف اصلی که اجرای FPGA به کمک جمع کننده های خط لوله است، به کمک شبکه عصبی عمیق کانولوشن، مدل سازی و یک شبیه سازی در محیط MATLAB به کمک خط فرمان و سیمولینک، انجام شده است و نتایج، حاکی از حالتی نزدیک به بهینه برای رویکرد ارائه شده را نمایش می دهد.

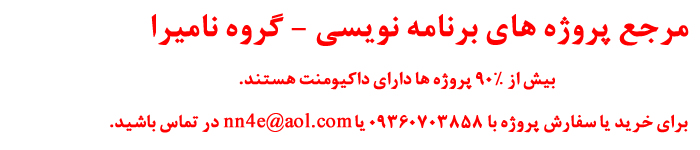

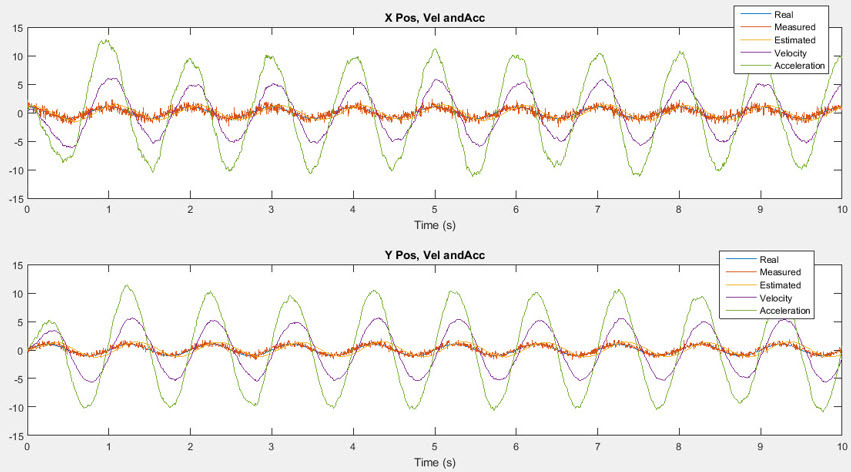

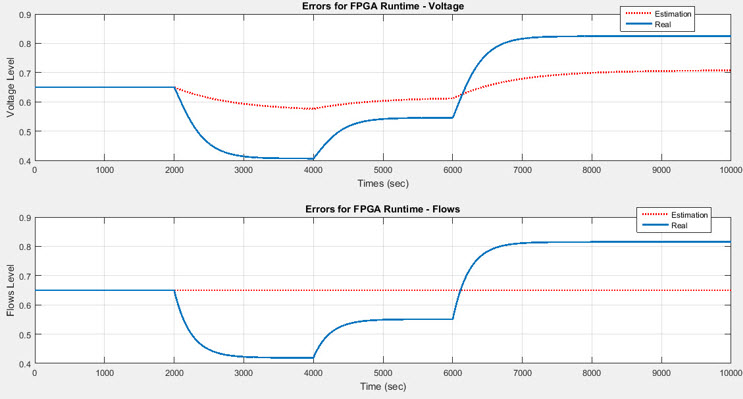

عکس خروجی برنامه

عکس 1

عکس 2

عکس 3

عکس 4

عکس 5

عکس 6

برای خرید این پروژه با شماره 09360703858

یا آدرس ایمیل nn4e@aol.com در تماس باشید.